Building the Future: What Construction Can Learn from Semiconductor Manufacturing

How incentives and capital generate extreme innovation in semiconductor manufacturing, and what the construction industry can learn.

The fascinating world of chips

Lately I’ve been fascinated by semiconductors. More specifically I’ve been obsessed with the manufacturing process, and even more specifically how the industry innovates and breaks barriers. This interest has been heightened by the fantastic book “Chip Wars: The Fight for the Worlds Most Critical Technology” by Chris Miller - highly recommended reading.

Semiconductors, “chips”, are ubiquitous in our lives. We use technology all day and everyday which are dependant on chips. The world is now completely reliant on their production and on their continued evolution and improvement. The amount of transistors on a chip is the metric in which progress is measured, and is driven by what has been coined as Moore’s Law:

“Moore's law is the observation that the number of transistors in an integrated circuit (IC) doubles about every two years. Moore's law is an observation and projection of a historical trend. Rather than a law of physics, it is an empirical relationship. It is an experience-curve law, a type of law quantifying efficiency gains from experience in production.” (https://en.wikipedia.org/wiki/Moore%27s_law)

In order to maintain this pace of development chip designers and manufacturers must innovate constantly, challenging technological boundaries in order to breakthrough constraints.

What has this got to do with construction you may ask…. Well, not much, but looking at the market pressures and technological challenges of chip manufacturing shines a stark light on construction. But that’s for later, first Chips.

Chip Factories

When Integrated Circuits, Semiconductors, or Chips were first invented and used in technology manufacturers had an integrated business model. They designed, manufactured, tested and sold the products they made. However, due to the expense on the manufacture side (of refitting and replacing equipment used in manufacture to keep up with development) some business disintegrated the model.

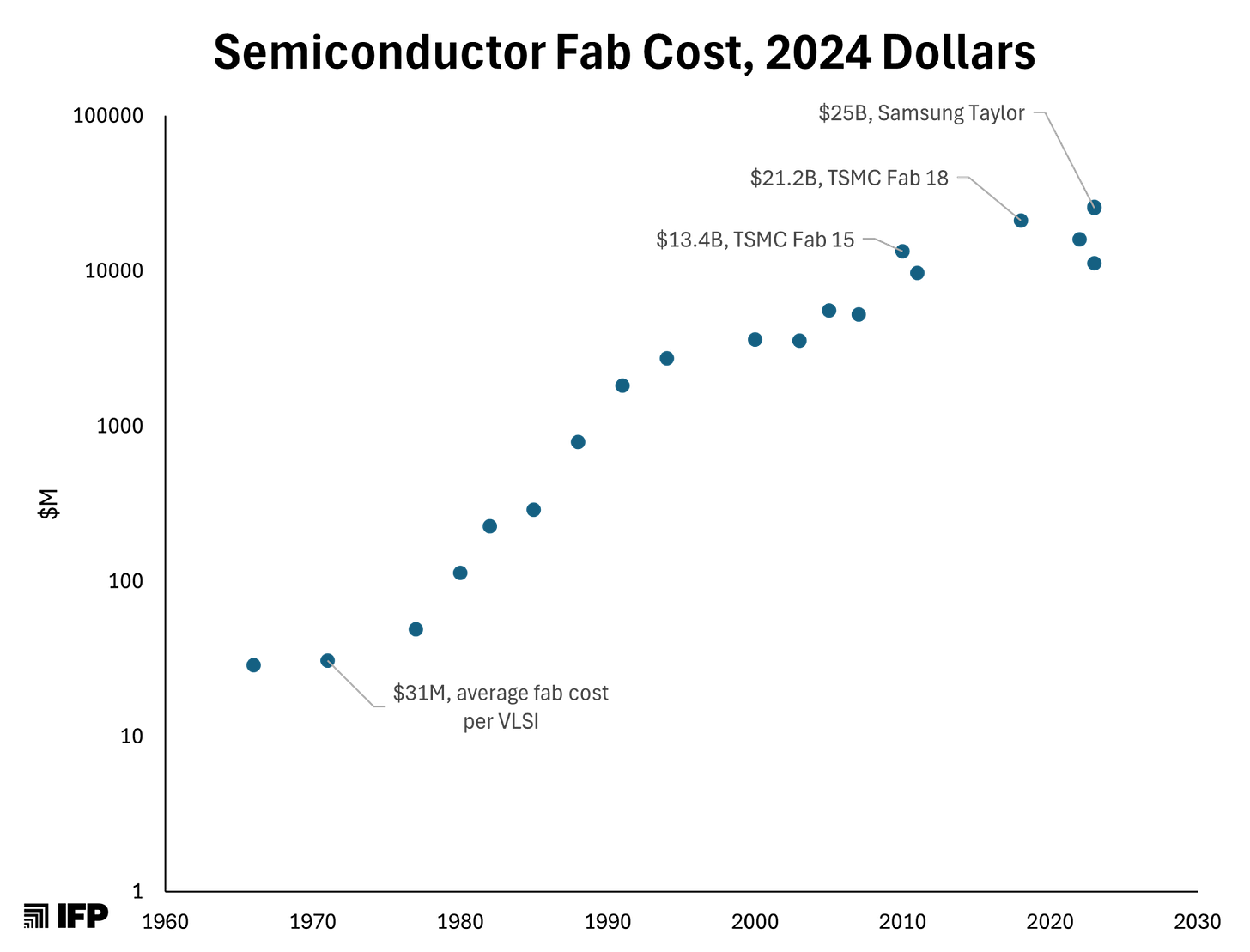

Chips are manufactured in a Fab (Semiconductor Fabrication Plant). These are incredibly advanced ‘factories’ and as such are complex and expensive facilities to build. Today a modern Fab can cost $10-20 billion to get from concept to production. A significant amount of that expense is the equipment used to manufacture the Chips. Cost have steadily increased in the fabrication process dictating the disintegrated, or “Fabless” and “Foundry”, business model prevalent today.

The above graph shows Fab construction costs as shown in “How to build a $20 Billion Dollar Semiconductor Fab” by semiwiki.com

The design and manufacture of chips is usually split between those who design chips and those who fabricate them. Designers are numerous and range from small independent companies to large conglomerates. Apple, Tesla, AMD, Nvidia being key names today.

On the other side of the Fabless model are the Foundries. These are companies who specialise in the manufacture of those designs. Essentially, anyone can join the queue and have their Chip design become a reality by placing an order with a Foundry business. Pretty similar to General Contracting in construction.

Fabs are predominantly in Asian countries (namely China and Taiwan) as labour costs are typically lower than in countries where Chips are designed (USA and UK, for example).

Foundries normally work for multiple ‘Fabless’ businesses, allowing them to keep a full order book and, therefore, predictable demand and revenue. The biggest companies in the Foundry space are Taiwan Semiconductor Manufacturing Company (TSMC, Taiwan), Samsung (South Korea) and GlobalFoundries (spun out of AMD, USA).

There are still some integrated business models out there who design and manufacture their own Chips, the best known of these is Intel.

Though the design of semiconductors is fascinating my interest is in contractors of the chip world, Foundries. Why are they so expensive? How do they continue to keep up with Moore’s Law? How and why do they constantly innovate?

To start to get to the bottom of these questions we’ll need to look at how Chips are made.

Making a Chip

Chip Making Machines

The manufacturing of chips is similar to a construction project. There is a design, they are built in phases, have key materials, and there are machines used form the final product. The difference, of course, is the repeatable nature - with thousands to millions of the same design created in a manufacturing run.

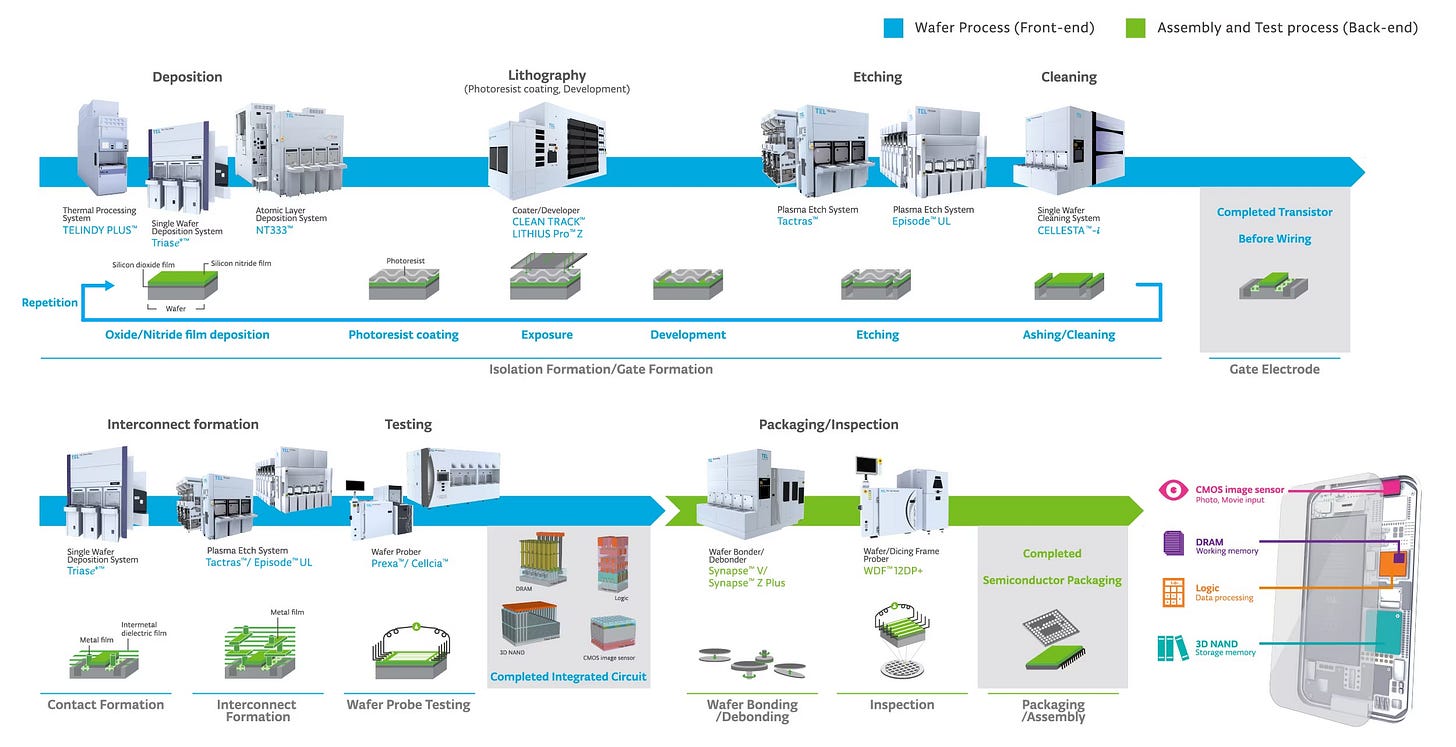

Here is a generic description of the chip manufacturing journey:

Building the Chip

Starting with the Wafer:

The process begins with a silicon wafer—a thin, circular disc. Silicon is a material used because it can easily conduct electricity when controlled, making it perfect for building electronic circuits.

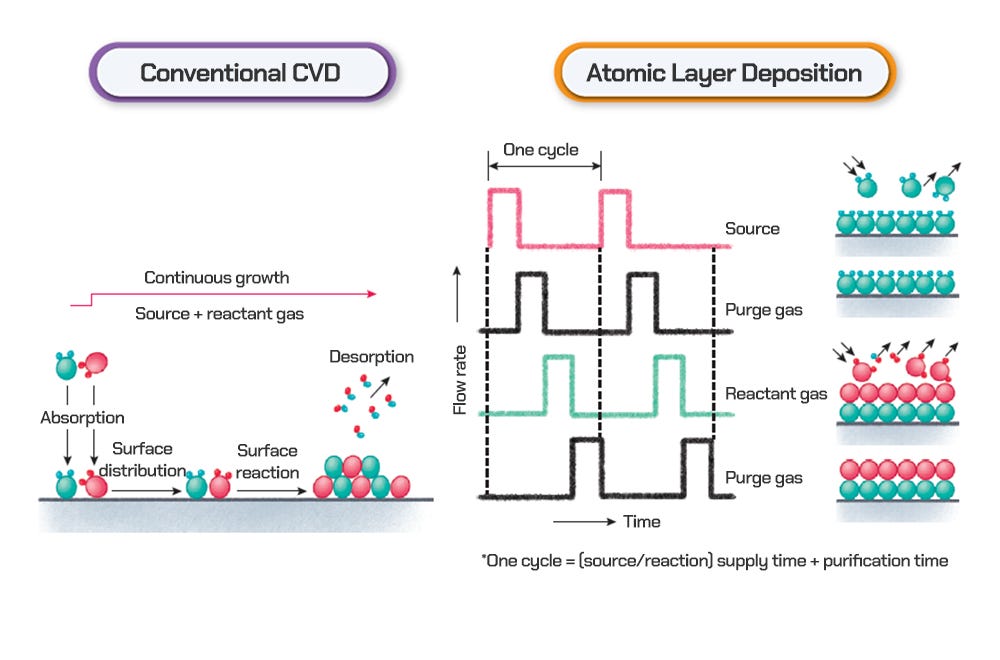

Layering the Materials (Deposition):

To prepare the wafer for circuits, several thin layers of special materials (like oxides and nitrides) are added. These layers help create the components that will store and move electric signals across the chip. This process is called deposition and is done with highly controlled machines.

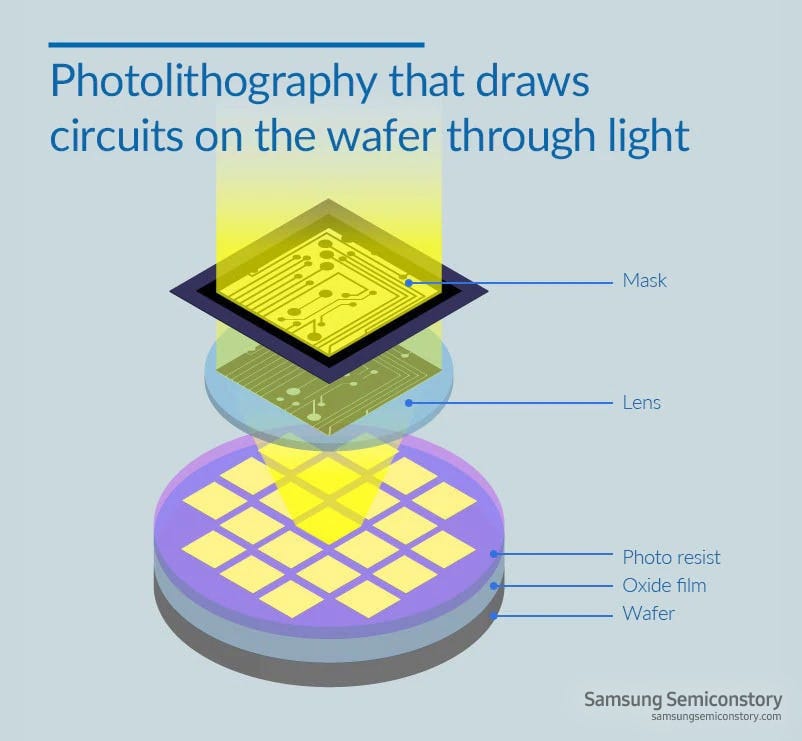

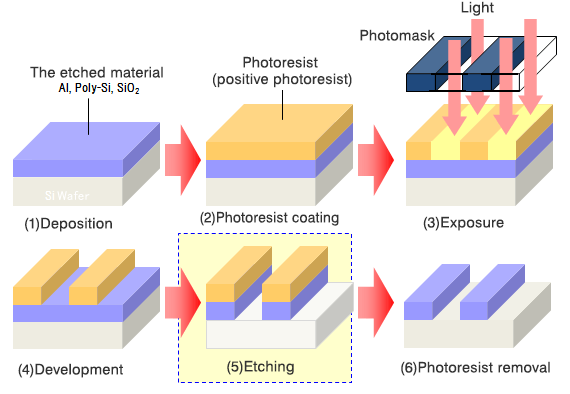

Creating the Circuit Patterns (Lithography):

Now it’s time to draw the layout of the circuits. The wafer is coated in a light-sensitive material called photoresist. Using a special machine, precise light patterns are shone onto the wafer, which creates the blueprint for the circuits.

Carving the Design (Etching):

After the pattern is exposed to light, the parts we don’t need are chemically removed through a process called etching. Like earthworks, pathways and spaces are carved out where the electrical signals will flow on the chip.

Cleaning the Wafer:

Once etching is done, the wafer goes through a cleaning process to remove any unwanted debris or residue. This ensures that the next layers can be added smoothly without contamination.

Repeating to Build Layers:

The same process—deposition, lithography, and etching—is repeated many times. Each time, new layers are added to build different parts of the chip, like the transistors and connections between them. Each layer adds complexity to the chip, like adding floors to a skyscraper.

Connecting and Testing the Chip

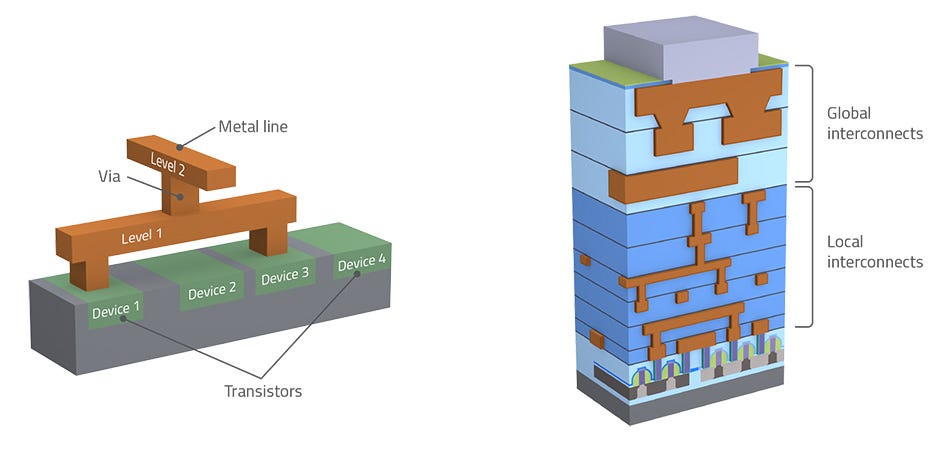

Building the Connections (Interconnect Formation):

After creating the transistors (the tiny switches that control the flow of electricity), they need to be connected so they can work together. This involves adding very fine metal wires to form pathways, allowing signals to move from one part of the chip to another.

Testing the Chip:

Before the wafer is cut into individual chips, it is tested. Using tiny probes, the circuits are checked to ensure they are working as intended.

Cutting and Packaging:

Once testing is complete, the wafer is cut into individual chips. Each chip is carefully packaged to protect it from physical damage, dust, and moisture. Packaging also helps with heat management, which is crucial because chips get hot when used in devices.

The Final Chip:

The final chip contains different components: memory for storing data (like DRAM and 3D NAND), processing units for executing commands (called logic), and other specialized parts like CMOS image sensors for capturing photos.

The image below from Tel.com graphically shows the manufacturing process.

A key element not covered in the above is the building itself. Its location is key, with specific needs around ground conditions, transport connections, and power & water supply. Another key aspect is cleanliness. Fabs must be carefully managed to ensure that dust and other particulate do not interfere or sabotage the incredibly sensitive equipment and products.

For more detail on building a Fab I’d highly recommend Brian Potter’s article ‘How to Build a $20 Billion Semiconductor Fab’.

As you begin to take in the detail, you see that Making a chip is a complex and multifaceted business. There are many processes, all contributing to the quality of the final product. These processes are housed in complex buildings, and use intricate tooling to meet the demands of scale and speed. This tooling is where the innovation lies - to maintain Moore’s Law the tools need to constantly improve - which means, the industry and its supply chain must continually innovate.

Economy of scale

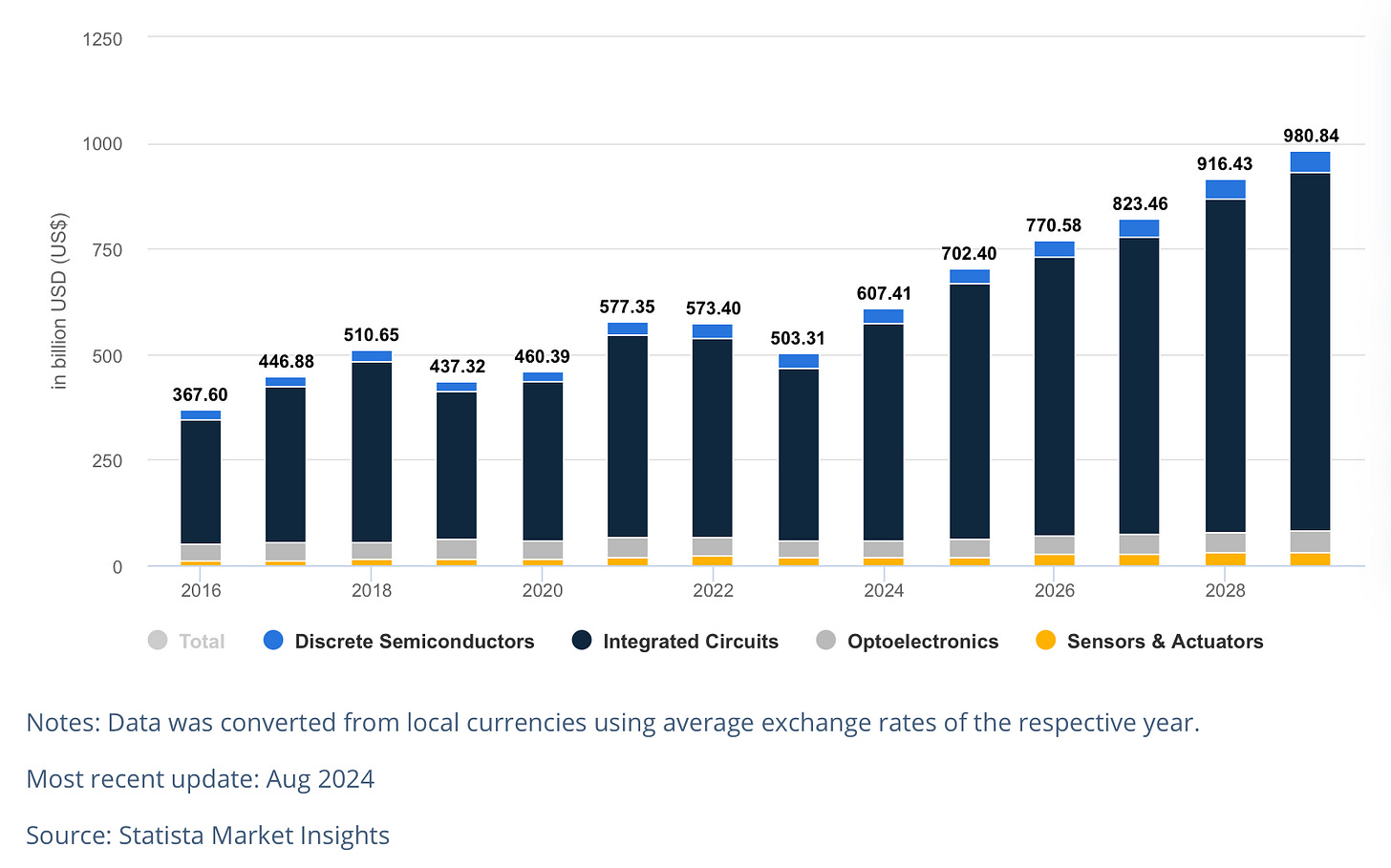

Our economy is effectively driven by semiconductors. Items like cars, trains, planes, smartphones, computers, all the way to your toaster and dishwasher use chips. These devices power industries which our economy is built on - transport, finance, commerce, farming, construction…

As technology gets ever more powerful, smaller, and energy-efficient the Chips used must evolve to keep pace.

Therefore, we are completely beholden to technological advances in chip technology and it’s keeping pace with Moore’s Law. This means that there is a huge incentive for investment in R&D for the semiconductor supply chain. The demand will always be there, and if a company makes a breakthrough it may make a huge leap across it’s competitors. The sheer capital at play in the industry is staggering. The global market for 2024 is expected to reach over $600b (Statista).

Anything is possible with the right incentive and capital.

Innovate, or die.

Due to global demand for progress, innovation in the semiconductor industry is a business critical issue. If a Foundry, designer, or tool supplier misses a key development they can find themselves out of business. The only consistent in life is change, and in semiconductors this is on steroids. There is an ever quickening quest to find competitive advantage in an industry where last years bleeding edge is this year’s low priced commodity.

An amazing example of innovation and competitive advantage in chip manufacturing is in lithography tooling. Let dive into how a small firm in the Netherlands changed the world as we know it.

ASML: “Extreme” Innovation

What is lithography?

As we established earlier, lithography is a critical process in semiconductor manufacturing that involves transferring a pattern from a photomask (think stencil) onto the surface of a silicon wafer. This pattern defines the intricate circuits and features of microchips. The process uses light to project the pattern onto a light-sensitive material (photoresist), which is then chemically treated to create the necessary structures on the wafer. The precision of this process directly determines how small and efficient the semiconductor components can be, making lithography one of the most essential stages in chip production. The finer your structure, the more transistors you can fit on the chip - making lithography a key component to Moore’s Law.

Who are the players?

The global semiconductor industry is highly competitive, with key players in different segments. In lithography, the primary companies involved are ASML, Nikon, and Canon. Nikon and Canon were once the leaders in traditional lithography methods, but have found it difficult to compete at the leading edge due to ASML’s technological breakthroughs.

A history of innovation

Lithography has undergone significant innovation over the past few decades. Initially, Deep Ultraviolet (DUV) lithography, which uses 193nm light (nanometre = one billionth of a meter), was the standard. However, as the industry demanded ever-smaller feature sizes to enable more powerful and energy-efficient chips, this technology hit its physical limits. A breakthrough was required to continue scaling down semiconductor components, which led to the development of Extreme Ultra Violet (EUV) lithography. EUV uses light with a much shorter wavelength of 13.5nm, enabling the creation of smaller and more complex transistor designs.

Extreme Ultra Violet

ASML (Advanced Semiconductor Materials Lithography) revolutionised the semiconductor industry with its EUV lithography machines. The development of EUV technology is one of the world’s greatest engineering breakthroughs, requiring collaboration and a financial investment which spanned decades and consumed billions of dollars. Key partnerships with companies like Intel, TSMC, and Samsung were crucial to overcoming the scientific hurdles that had previously made EUV lithography impossible to implement on a commercial scale.

Guiding lights

One of the most significant breakthroughs in EUV technology was the development of the light source. EUV lithography requires light with a wavelength of just 13.5 nanometres, which is far shorter than the deep ultraviolet (DUV) light used in previous generations of lithography. The challenge is that light at this wavelength does not naturally occur in a stable, high-intensity form. ASML, in partnership with Cymer, Trumpf, and others, developed a laser-produced plasma (LPP) light source that could generate the necessary EUV light. In this system, powerful lasers are fired at droplets of molten tin, which are vaporised to create a plasma that emits EUV light. This process requires extreme precision and immense energy, with the laser firing at 50,000 pulses per second to ensure a continuous, high-intensity light source. Developing a light source powerful and stable enough to be used in a manufacturing environment was a colossal achievement, requiring years of iteration and fine-tuning.

Holding up a mirror

Another critical breakthrough was the development of mirrors that could handle EUV light. Unlike traditional lithography, EUV cannot use lenses to focus light because the material at this wavelength is absorbed by glass. Instead, EUV systems rely on highly specialized mirrors to reflect and focus the light. These mirrors, developed by ASML in collaboration with German optics company Zeiss, are the flattest and most precise ever made. The surface of each mirror must be accurate to within a fraction of a nanometre to effectively reflect EUV light. Any minor imperfection could scatter the light and ruin the lithography process. The mirrors are coated with multiple layers of molybdenum and silicon, which help reflect the EUV light with minimal absorption. Developing this reflective coating and ensuring the mirrors’ extreme precision was a technological feat that required unprecedented levels of engineering and optical science.

Bills to pay the skills

These technological advances, however, came with a hefty price tag. ASML and its partners poured billions into research and development to make EUV lithography a reality. Intel alone invested over $4 billion into ASML’s EUV program, while TSMC and Samsung made similar investments to ensure they would have access to this cutting-edge technology. Each machine costs over $150 million and consists of more than 100,000 parts sourced from over 5,000 suppliers worldwide.

The complexity of EUV systems extends beyond the light source and mirrors to encompass the entire infrastructure needed to operate them. Each machine weighs more than 180 tons and requires highly specialised installation and maintenance, further reinforcing ASML’s competitive advantage. EUV lithography has become indispensable for producing the most advanced chips. By leading innovation in this space, ASML has secured its place as the dominant supplier of EUV machines, reshaping the semiconductor industry and setting the stage for continued advancements in chip manufacturing.

Monopolising the industry

ASML’s dominance in the EUV market has effectively created a monopoly in the most advanced segment of lithography. The company is currently the only supplier of EUV machines. Because of the significant technological barrier to entry, no other company has been able to match ASML’s EUV capabilities, giving them a unique competitive advantage. As semiconductor manufacturing increasingly relies on EUV for advanced node production, ASML’s monopoly in this sector will likely persist, reinforcing its role as a gatekeeper to the future of semiconductor innovation.

Lessons for Construction

Anything is possible with the right incentive and capital.

Let me be clear, there are clear differences between the semiconductor industry and construction:

Construction does not have the free capital nor the immediate demand for technological breakthroughs of semiconductors.

Semiconductor manufacture is highly repeatable. They produce thousand to millions of the same design.

But construction does have its own drivers - which are becoming more critical as time passes. Climate change, aging stock of buildings and infrastructure, and growing demand on computing power are market drivers for the industry. Add to this the issues we have around productivity and skilled workers - pressure is slowly building which I believe will force a rethink and reordering to reward those with the capability and capacity for rapid innovation.

A strategy of consistent incremental improvements

The fight to prolong Moore’s Law is a constant driver for innovation as chips need smaller and smaller components to keep up with demands on performance and energy-efficiencies. We don’t have a similar concept in construction, but we all know that inefficiencies and cost increase cannot be tolerated forever in construction.

In the absence of an external force to drive consistent innovation, companies in the industry need to find ways to drive incremental improvements. This may be through digital, technological, engineering, process, and business model innovations.

Companies need to challenge themselves by setting ever increasing performance goals which leaders and teams are incentivised to meet. The strategy should not be ‘to innovate’ as we see all too often. A strategy is a solution to an addressable problem. Therefore innovation should be driven by strategies to specific challenges with the aim of increasing performance.

And let’s not forget, ASML spent $10+ billion to develop EUV. Whilst this is unfathomable in construction innovation cannot happen without capital investment.

Specific Knowledge Capture

Chip manufacture has rewarded businesses who have invested heavily in R&D. We’ve seen that ASML, along with it’s investors, have effectively monopolised cutting edge technology and made themselves the only game in town when it comes to EUV machines.

Construction firms have historically struggled with internal R&D. The profit margins are prohibitive and the future less ‘forecastable’ in terms of demand. But, all it takes is one disruptor to break the mould and take a long term view.

It doesn’t have take $billions. What is critical is simply building systems to allow the enterprise to consistently learn from information and continually improve going forward. With the dawning of AI, captured knowledge will become much easier to surface by the individual. Tools such as Large Language Models coupled with GraphRAG are making this very accessible to all organisations, regardless of size.

An effort by system architects and Chief Data Officers (CDOs) to integrate and structure the organisations knowledge to make capturing and then surfacing knowledge in a seamless, accessible, way should be prioritised.

Further, once organisations are capturing that information they need to ensure they are protecting and using it to provide a competitive advantage. For example, investment in bespoke development software based on the organisations specific knowledge could unlock huge untapped value. Such breakthroughs, driven by need, which capture specific or tacit knowledge as intellectual property in a product or system would be a huge differentiation not available to competitors.

Business Model reform

The semiconductor industry started with a vertically integrated structure. But soon disruptors found that specialising in a part of the value chain could provide opportunity for profit.

Construction is not fully vertically integrated but we do have an industry which is top heavy with generalists, with the specialists sitting in Tier 2 of the supply chain and below. This model is ripe for disruption.

Our standard model is that of a pyramid. Lower level specialist suppliers roll up to lighter level, large, generalists who effectively aim to ‘integrate’ the project team through central control. In this model the money generally flows down, along with the risk. However, is the most effective project model which we account for modern technology and practice?

In the future specialists could be more directly contracted to an ‘integrator’ model which is supported by Information Management, utilising technology to validate, consolidate, and coordinate critical engineering, contractual, and project management information. Project 13 is a step towards this model.

What next?

So where does this leave you and construction? For me personally, the delve into the semiconductor industry has highlighted the need to find the repeatable, utilise development cycles, and look for areas of specialisation which can be differentiated and disrupted. Construction is a vastly different industry to producing chips but there are lessons to draw parallels and learn from.

I’m incredibly interested in your thoughts on this. Please do reach out, let's talk, and bring some of this to life.

This felt like an Asianometry episode!